## Formalising the State Machine Modelling Tool (SMMT)

**MASTER THESIS**

Goirle December 1, 2023

### J.E.P.M. van Laarhoven

TU/e Student ID: 1230803 info@jordivanlaarhoven.nl j.e.p.m,v.laarhoven@student.tue.nl jordi.vanlaarhoven@cpp.canon Supervisors Dr. Ir. T.A.C. Willemse<sup>1</sup> Dr. Ir. L.C.M. van Gool<sup>2</sup>

Ir. O. Bunte<sup>1</sup>

Version

1.0.2

1 Eindhoven University of Technology, Eindhoven, The Netherlands 2 Canon Production Printing, Venlo, The Netherlands

Canon

The writer was enabled by Canon Production Printing Netherlands B.V. to perform research that partly forms the basis for this report.

Canon Production Printing B.V. does not accept responsibility for the accuracy of the data, opinions and conclusions mentioned in this report, which are entirely for the account of the writer.

## Abstract

Model-Driven (Software) Engineering (MDSE) is gaining popularity in industry. More and more companies acknowledge the benefits of using MDSE to develop their software components. A company that exploits model-driven software engineering is Canon Production Printing (Venlo, The Netherlands). At Canon Production Printing, the State Machine Modelling Tool (SMMT) was developed to enable the modelling of software components using state machines. In this graduation report, we present SMMT and formally define a subset of the SMMT language. A translation from SMMT specifications to mCRL2 specifications is defined to allow for model checking on the SMMT specifications. We show that this translation can correctly generate mCRL2 specification for the existing SMMT specifications at Canon Production Printing. Furthermore, we show how the mCRL2 toolset can be used to prove the correctness of SMMT specifications.

## Contents

| 1 | Intr       | duction                                            | 1        |

|---|------------|----------------------------------------------------|----------|

|   | 1.1        | Related Work                                       | 1        |

|   |            | 1.1.1 Open Interaction Language (OIL)              | 2        |

|   |            | 1.1.2 Dezyne                                       | 2        |

|   |            | 1.1.3 Coco                                         | 2        |

|   |            | 1.1.4 Event-B                                      | 2        |

|   |            | 1.1.5 CERN                                         | 3        |

|   |            | 1.1.6 Cordis SUITE                                 | 3        |

|   |            | 1.1.7 Executable UML Specifications                | 3        |

|   |            | 1.1.8 Internet of Things                           | 3        |

|   | 1.2        | Problem Statement                                  | 4        |

| 2 | Stat       | e Machine Modelling Tool                           | 7        |

| - |            | Introduction to SMMT                               | 7        |

|   |            | SMMT Constructs                                    | 8        |

|   | 2.2        | 2.2.1 Name and Namespace                           | 9        |

|   |            | 2.2.2 Events                                       | 9        |

|   |            |                                                    | 10       |

|   | 2.3        |                                                    | 15       |

|   |            |                                                    |          |

| 3 |            |                                                    | 17       |

|   | 3.1        | <b>J</b>                                           | 17       |

|   |            |                                                    | 17       |

|   |            | ··· <b>]</b> ··· · · · · · · · · · · · · · · · · · | 18       |

|   | ~ ~        |                                                    | 20       |

|   |            | · · · · · · · · · · · · · · · · · · ·              | 20       |

|   | 3.3        | Conclusion                                         | 20       |

| 4 | Mat        | nematical Preliminaries                            | 23       |

| 5 | Far        | nal Definition of SMMT                             | 25       |

| 5 | 5.1        | Abstract Syntax of an SMMT Specification           |          |

|   | 5.2        |                                                    | 27<br>31 |

|   | 5.2<br>5.3 |                                                    | 36       |

|   | 5.5        |                                                    | 37       |

|   |            | 5.3.2 Semantics of an SMMT Specification           |          |

|   |            |                                                    | 50       |

| 6 | Trai       |                                                    | 49       |

|   |            |                                                    | 49       |

|   | 6.2        |                                                    | 51       |

|   |            |                                                    | 52       |

|   |            | 6.2.2 Validation Checks on the SMMT Specification  |          |

|   |            | 6.2.3 Translation of Definitions to Mappings       | 59       |

|   | 6.2.4                                                  | mCRL2 Process Specification                                                                                                                                                                                                    | 60                               |  |  |  |  |  |  |  |  |

|---|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|--|--|

| 7 | 7.1.1<br>7.1.2<br>7.2 Prope<br>7.2.1<br>7.2.2<br>7.2.3 | nts         ctness of the SMMT2MCRL2 Translation         Verification Approach         Results Correctness Verification SMMT2MCRL2         erty Verification         Properties         Approach         Results         usion | 63<br>71<br>76<br>76<br>78<br>78 |  |  |  |  |  |  |  |  |

| 8 | Conclusio                                              | n                                                                                                                                                                                                                              | 83                               |  |  |  |  |  |  |  |  |

| 9 | Future Research 85                                     |                                                                                                                                                                                                                                |                                  |  |  |  |  |  |  |  |  |

| Α | Proofs for Chapter 5 89                                |                                                                                                                                                                                                                                |                                  |  |  |  |  |  |  |  |  |

| В | mCRL2 Specification of Figure 5.3 105                  |                                                                                                                                                                                                                                |                                  |  |  |  |  |  |  |  |  |

| С | Complete mCRL2 Specification 11                        |                                                                                                                                                                                                                                |                                  |  |  |  |  |  |  |  |  |

|   |                                                        |                                                                                                                                                                                                                                |                                  |  |  |  |  |  |  |  |  |

# Chapter 1

## Introduction

Model-Driven (Software) Engineering (MDSE) is gaining popularity in industry. More and more companies acknowledge the benefits of using MDSE to develop their software components. One advantage of MDSE is that it raises the level of abstraction. This simplifies the development of complex components, which increases the productivity of the software engineers. Another major benefit of using MDSE is that it opens the door to model checking. Using the created models, model checkers can be used to analyse whether certain properties are satisfied by a model, properties that may not be verifiable using test cases. Both advantages result in a more cost-effective approach.

A company that exploits model-driven software engineering is Canon Production Printing (Venlo, The Netherlands). One of the modelling languages that has been developed over the years is the Open Interaction Language (OIL). OIL is a modelling language that is intended to express the behaviour of control-software components, which is not limited to printers. The semantics of the Open Interaction Language has been formally defined, which allows a translation from specifications in OIL to mCRL2 model specifications.

The mCRL2 model checker is developed by the Eindhoven University of Technology and consist of both a language [1] and a powerful toolset [2]. The mCRL2 language is used to describe the behaviour of processes based on the algebra of communicating processes [3] that is extended with data. Among others, the tool enables the generation and reduction of the state space of an mCRL2 specification. Using the toolset, one can verify whether properties are satisfied for the given specification.

This graduation project concerns the State Machine Modelling Tool (SMMT). SMMT is a tool and modelling language developed at Canon Production Printing to model the behaviour of software components using state machines. Executable C++ and C# code can be generated from the SMMT specifications. Unlike OIL, SMMT has not been developed with a focus on creating a formally defined language to allow for model checking. Instead, SMMT was developed to closely resemble the state machines of the existing Boost Statechart C++ library [4, 5] but with some of the additional expressive power of OIL.

In the remainder of this chapter, we discuss related research (Section 1.1) and introduce the research question that serves as a basis for this graduation project (Section 1.2).

### 1.1 Related Work

In this section, we discuss a selection of domain specific programming languages of which the semantics have been formalized and that are translated to the mCRL2 language or the language of other model checkers for automatic property verification. We discuss research that has been performed on the analysis, translation and verification of languages based on state machines.

### 1.1.1 Open Interaction Language (OIL)

A language that is closely related to SMMT is the Open Interaction Language (OIL) by L. van Gool. OIL and SMMT are both domain specific modelling languages developed within Canon Production Printing. Using OIL, the behaviour of control-software components can be specified, analysed, and visualized. In "Formal verification of OIL component specifications using mCRL2", O. Bunte et al. [6] defined the formal semantics of OIL specifications. A translation to mCRL2 specifications with the same behaviour as the OIL specification has been defined, based on the formal operational semantics. Using the mCRL2 toolset [2], properties can be expressed using the first-order modal mu-calculus and automatically verified on a given mCRL2 specification. OIL specifications are originally based on XML. A domain specific language has been designed and implemented by J. Denkers et al. [7] which, together with some additional syntactic sugar to OIL, creates a more user-friendly way to specify components using OIL. This DSL has been implemented using the Spoofax language workbench [8]. Using both the XML and DSL syntax of OIL, C++ code can be automatically generated, the correctness of which has partially been verified [6]. An experimental code generator has been implemented by M. Frenken [9] and has been optimized by T. Buskens [10].

#### 1.1.2 Dezyne

Another modelling language that has been formalized is the Dezyne language by the company Verum [11]. The Dezyne toolset allows engineers to specify and design software systems. Furthermore, the toolset allows for formal verification. In "Formalising the Dezyne Modelling Language", R. Beusekom et al. [12] formalised the Dezyne language by encoding the language in the mCRL2 process algebra [1]. In this paper, Beusekom et al. discuss the grammar of the Dezyne language using the Extended Backus-Naur Form (EBNF), which is a notation to denote the grammar of a language, standardized in ISO/IEC 14977 [13]. For each of the constructs in the Dezyne language a transformation to the mCRL2 language is introduced and a sketch of the formalisation of the execution semantics is presented. Using the Dezyne language executable code can be generated.

### 1.1.3 Coco

Another platform that aims at simplifying the development of software components is the Coco platform by Cocotec [14]. Using their Coco language, the behaviour of systems can be modelled. The tool uses the internally developed model checker FDR4 [15] which can automatically verify whether certain properties are satisfied in the model. The tool offers a graphical interface for debugging the models. Using UML sequence diagrams, traces can be visualized to show how a property is violated. From the Coco models, executable C++ code can be generated.

#### 1.1.4 Event-B

In "Formal verification and validation of run-to-completion style state charts using Event-B", K. Morris et al. [16] present how they formally verified and validated state charts using Event-B and Rodin. Morris et al. discuss a new notation for state chart modelling, on which the Event-B toolset is used for theorem proving. The Event-B tooling is supported by the Rodin platform, that is used for refinement and mathematical proofs. A scenario-based approach is introduced, based on the ProB model checker. Certain scenarios can be recorded and replayed to check whether states changed since the original run of the scenario. The Rodin theorem prover automatically verifies whether invariant properties are satisfied on the models. They also provide a complementary way to verify the model using the LTL model checker. This procedure allows to check for expected reactions to environmental triggers.

#### 1.1.5 CERN

Another organization that adopted the MDSE approach is CERN. For their Large Hadron Collider (LHC), state machines are used to generate executable code. In "Formalising and analysing the control software of the Compact Muon Solenoid Experiment at the Large Hadron Collider", Y. Ling Hwong et al. [17] formalised the semantics of the state machines by converting the state machines to the process algebra language of mCRL2. Using the translation from state machines to the mCRL2 process algebra language and the formal semantics, Ling Hwong et al. were able to develop tooling for checking whether certain properties hold on each state machine in isolation. Using their translation to mCRL2, various bugs were found in the models, which have been solved since.

#### 1.1.6 Cordis SUITE

Various papers have been published on formalising models based on UML models. As SMMT is based on state machines, it is therefore interesting to investigate papers that discuss translation of UML models to mCRL2. An example of such a language is the Cordis SUITE. In "Formal Verification of an Industrial UML-like Model using mCRL2", A. Stramaglia and J. Keiren [18] present how they formalised the semantics of the Cordis SUITE, which is a low-code developing platform for machine-control applications that is based on UML models. A translation from the Cordis models to the process algebra language of mCRL2 has been defined, based on the semantics of the Cordis language. In the paper, Stramaglia and Keiren show how powerful the usage of model checkers like mCRL2 is, through an experiment (Pneumatic Cylinder) in which bugs were found in the generated mCRL2 model and its implementation.

#### 1.1.7 Executable UML Specifications

In "Towards model checking executable UML specifications in mCRL2", H. Hansen et al. [19] present their translation for translating executable UML specifications to mCRL2 specifications. In the earlier mentioned research projects, properties on the generated mCRL2 models were directly performed using the first order modal mu-calculus using the mCRL2 toolset. In the paper by Hansen et al., tooling is presented that allows the software engineer to inspect error traces using UML sequence diagrams, instead of a labelled transition system. Using their toolset, the software engineer can express the expected behaviour as a UML state machine. In this state machine, the engineer can add "error" actions for behaviour that is not expected to happen. In this way, checking whether some safety property is satisfied in a model boils down to a reachability check for such "error" actions in mCRL2. Unfortunately, their system only allows the verification of safety properties but not liveness properties. Liveness properties would require the use of temporal logics.

#### 1.1.8 Internet of Things

In "The AbU Language: IoT Distributed Programming Made Easy", M. Pasqua et al. [20] introduce a domain specific language that can be used to control IoT devices. The language is built on the Attribute-based memory Updates communication model which is an extension of the ECA rules-based system. ECA systems use Event-Condition-Action rules for controlling the IoT device. The AbU language enhances the ECA rules with an interaction mechanism where communication is similar to broadcasting. However, not all communication is sent via a central processing infrastructure. Instead, decentralized edge servers are used.

The AbU language is a domain specific language in which programs can be developed consisting of a list of IoT devices, a list of type declarations and a collection of ECA rules. A device declaration covers the name and description of the device, as well as all details

about the resources of the device such as in- and output resources, an invariant that must be maintained and references to a set of ECA rules. Type declarations specify several custom types that can be used in the device specification. The ECA rules specify the behaviour of the devices. The language is event driven, when an event occurs for which a rule has been defined and the condition of that rule is satisfied, the action that is defined by the ECA rule is performed.

In the paper, M. Pasqua et al. first introduce the syntax of the AbU language. After which the formal operational semantics of the AbU language is presented. Experiments are discussed which show the effectiveness of the AbU language. Unfortunately, there is no support for model checking or other verification tools. Hence, it is not possible to verify whether certain properties hold in a AbU model/specification. In the future work section, the authors show interest in implementing a verification approach based on temporal logic like CTL or mu-calculus to allow for verification.

#### 1.2 Problem Statement

In this section we present the research question that will serve as a basis for this master's graduation project at the Eindhoven University of Technology. In this project, we perform research on the State Machine Modelling Tool (SMMT).

SMMT is a tool that can be used to model the behavior of complex software components using state machines. As mentioned before, SMMT has been developed with a focus to closely resemble the existing Boost C++ library. There exists no formal definition of SMMT. As the available documentation of SMMT does not cover all constructs of the language, it remains unclear for the engineers at Canon Production Printing how certain behavior can be modelled using SMMT. As a consequence, engineers may model behavior of software components in SMMT of which the expected behaviour does not correspond to the actual behaviour.

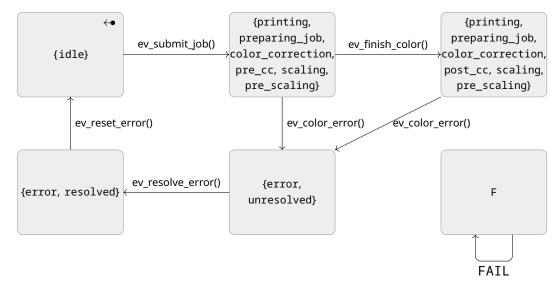

A testing library has been developed to determine the correctness of the existing SMMT specifications. The testing library requires the engineer to specify the behavior that they want to test on an SMMT specification as a separate SMMT specification. The test SMMT specification sends events to the SMMT specification and defines the correctness based on the responses received from the SMMT specification. According to the engineers that are familiar with the testing library, this approach to determine the correctness of an SMMT specification is time-consuming and error prone. Furthermore, there are limitations on what properties can be checked on an SMMT specification using the testing library. A formal definition of SMMT would allow us to define a translation from SMMT specifications to mCRL2 specifications. Using such an mCRL2 specification, the engineer can verify whether certain properties hold on the specification. Furthermore, there exist various restrictions that must be satisfied by each SMMT specification that are not checked by the implementation of SMMT in MPS. The translation from SMMT specifications to mCRL2 specifications to mCRL2 specifications to automatically verify whether these restrictions as defined in the generated mCRL2 specification hold for each SMMT specification.

The aim of this graduation project is to answer the following research question:

#### "To what extent can we formalise and prove the correctness of SMMT specifications using the mCRL2 model checker?"

To formalise and prove the correctness of SMMT specifications, we first performed an analysis of SMMT. In this analysis we discuss how the engineers at Canon Production Printing experience SMMT and discuss the insights we gained from the 26 SMMT specifications that have been developed at Canon Production Printing at the time of writing. The results of the analysis show the relevance of formally defining SMMT and defining a translation from SMMT specifications to mCRL2 specifications to allow for model checking. Furthermore, we

have analysed the relevance and frequency of the constructs of the SMMT language to determine the order in which the constructs of SMMT were formalised.

To formally define SMMT, we defined the syntax, static semantics and operational semantics of SMMT. A mathematical model has been defined that is used to represent an SMMT specification. The static semantics has been defined as a number of restrictions that must be satisfied on this mathematical model. Finally, the operational semantics of SMMT has been defined as a labelled transition system. Unfortunately, we have not able to formally define the complete set of constructs of the language of SMMT due to time constraints.

We have defined a translation that translates SMMT specifications to mCRL2 specifications. The mCRL2 specification that is generated from an SMMT specification closely correlates to the formal definition of SMMT. The generated mCRL2 contains a representation of the mathematical model of the SMMT specification. Using this representation of the mathematical model, we have defined mapping and equations that correspond to the validation checks and the functions that are used to define the operational semantics. The process specification of the mCRL2 specification correlates to the definition of the operational semantics.

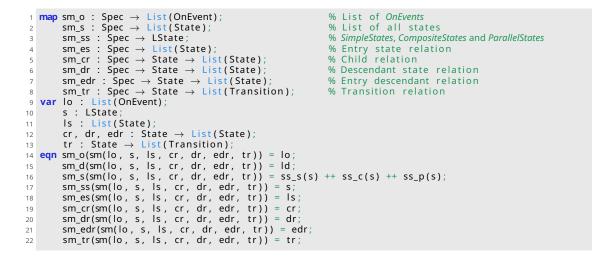

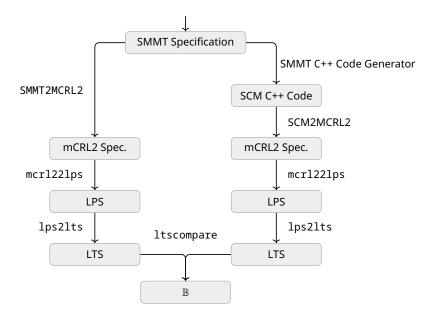

Various experiments have been performed to prove the correctness of the translation that we defined. We defined a translation to generate an mCRL2 specification from the generated C++ code that is generated by SMMT. Using the mCRL2 toolset, we have verified whether the behavior of the two mCRL2 specifications define the same behavior. These experiments have been performed on the 26 SMMT specifications that exist at the time of writing. We have shown that the translation is correct for 25 out of the 26 SMMT specifications and that the correctness could not be determined for 1 SMMT specification. Furthermore, several issues in the implementation of SMMT in MPS were found when performing these experiments. We have shown how properties can be checked on the generated mCRL2 specifications.

**Outline** This thesis is structured as follows. We first informally introduce SMMT in Chapter 2. Next, we discuss our analysis of SMMT in Chapter 3. In Chapter 4 we introduce several definitions that are used to formally define SMMT. We formally define a subset of the constructs of the SMMT language in Chapter 5. In Chapter 6, we introduce the mCRL2 model checker and toolset and we discuss the approach for defining the translation from SMMT to mCRL2 specifications. In Chapter 7 we discuss the experiments that we have performed to verify the correctness of the translation and to verify the correctness of the existing SMMT specifications. We discuss the results and answer the research question in Chapter 8. Finally, we discuss opportunities for future research in Chapter 9.

CHAPTER 1. INTRODUCTION

## **Chapter 2**

## **State Machine Modelling Tool**

The State Machine Modelling Tool (SMMT) is a modelling tool and language developed by Canon Production Printing that allows its user to model behavior of software components using state machines. Furthermore, SMMT enables the generation of C# and C++ code from these SMMT models. In this section we informally introduce the State Machine Modelling Tool. We discuss the history and the goal of SMMT in Section 2.1. In Section 2.2, we introduce the constructs of the SMMT language. To get some intuition on how the generated code of an SMMT specification behaves, we discuss how the events are handled during execution in Section 2.3.

### 2.1 Introduction to SMMT

At Canon Production Printing the Model-Driven Software development methodology was adopted a couple of decades ago. Using modelling software, models were designed consisting of state machines that modelled the expected behavior of software components. The engineers used these models to manually develop executable code that behaves according to the model. This workflow occasionally led to problems, as there was no coupling between the designed models and the code that was developed using these model. As a consequence, this process occasionally led to inconsistencies between the behavior as modelled by the state machine and the behavior of the developed executable code.

At first, the Boost C++ State Chart library was used to implement state machines. While this library enabled the modelling of simple state machines, it remained difficult to model the behavior of complex components. To simplify this workflow, two languages were developed. The first language that was developed at Canon Production Printing to simplify the modelling of software components using state machines is the Open Interaction Language (OIL). OIL was developed with a focus on creating a language with high expressive power that is formally well-defined. An advantage of having a formally well-defined language is that this enables model checking. This enables the engineer to check whether properties hold on their OIL specifications using a model checker. The engineers at Canon Production Printing developed the SCM C++ library that, in contrast to OIL, was not designed with a focus on creating a formally well-defined language. Instead, the aim of the SCM library was to create a library that closely resembles the existing state machines from the Boost C++ library but with some of the additional expressive power of OIL. To simplify the modelling of software components using the SCM C++ library, the State Machine Modelling Tool (SMMT) was developed using JetBrains MPS [21]. Using the State Machine Modelling Tool, state machines can be modelled both textually and graphically. Furthermore, the tool enables the generation of executable C++ and C# code from the models. The generated C++ and C# code makes use of the SCM library to implement the behavior of the state machines in that language.

### 2.2 SMMT Constructs

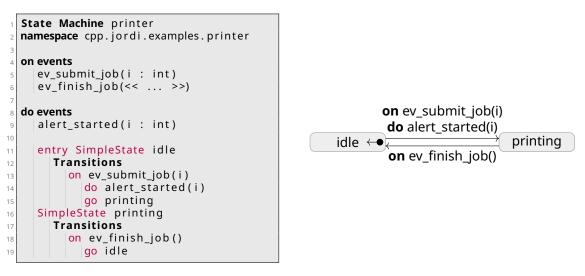

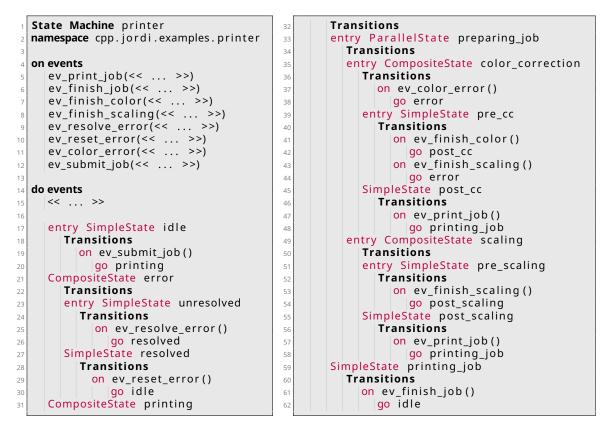

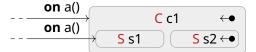

In this section, we introduce the constructs of the SMMT language. In SMMT, each specification represents a single state machine. An SMMT specification consists of five sections, as shown in figure 2.1, these are: a *name*, a *namespace*, a collection of *OnEvents*, a collection of *DoEvents* and a *region*.

| State Machine<br>namespace | e name<br>namespace |

|----------------------------|---------------------|

| on events                  |                     |

| (                          | OnEvents            |

| do events                  |                     |

| L                          | DoEvents            |

| A                          | Region              |

|                            |                     |

Figure 2.1: Overview of an SMMT Specification

SMMT has been implemented in JetBrains MPS [21] in which two representations have been developed that can be used by the engineer to model the behavior of a component as a state machine: a textual and a graphical representation. In all our examples we show both representations. In the graphical representation of SMMT, the section of the specification consisting of the name, namespace and lists of *OnEvents* and *DoEvents* is also shown. However, in our examples, we omit these details in the graphical representation to avoid repeating information.

In the remainder of this section, we introduce each section of an SMMT specification. To explain the constructs of the SMMT language, we gradually build an SMMT specification modelling the behavior of a simplistic printer. In Figure 2.2, an SMMT specification is given consisting of a single entry state called idle. The specification does not have any events or transitions.

| State Machine printer<br>namespace cpp.jordi.examples.printer |         |

|---------------------------------------------------------------|---------|

| 3<br>4<br>5 <                                                 |         |

| 6<br>7 <b>do events</b><br>8 <<>>                             | idle ←● |

| 9<br>entry SimpleState idle<br>Transitions                    |         |

(a) Textual Representation

(b) Graphical Representation

Figure 2.2: An SMMT specification representing a printer that is always idle

In the representations of an SMMT specification,  $\ll ... \gg$  denotes an empty field in which a component can be inserted. For example, this enables us to define *OnEvents* and *DoEvents* in lines 5 and 8 for the SMMT specification in Figure 2.2a respectively.

#### 2.2.1 Name and Namespace

As shown in Figure 2.1, each SMMT specification has a name and a namespace. The namespace is the fully qualified name of the SMMT specification,. That is, an SMMT specification can be identified by its namespace. The name is of type String, the namespace consists of one or more Strings separated by dots. Here, a String is defined as a value that corresponds to the regular expression  $[a-z]([a-z0-9_])^*$ .

In the running example (Figure 2.2) the name and namespace of the SMMT specification are defined on lines 1 and 2 of the textual representation respectively. That is, the name of the SMMT specification in the running example is printer and the namespace is cpp.jordi.examples.printer. Note that, the name and namespace do not depend on each other. That is, the name of the SMMT specification is not required to be contained in the namespace of the SMMT specification.

#### 2.2.2 Events

SMMT distinguishes two types of events, namely *OnEvents* and *DoEvents*. *OnEvents* are events that are produced externally and may cause transitions of the SMMT specification to fire that are defined for that *OnEvent*. On the other hand, *DoEvents* are actions produced by the SMMT specification that serve as a response to processed *OnEvent* actions. Both *OnEvents* and *DoEvents* can be parametrized, where each parameter is of boolean type or of a custom specified type. In both the graphical and textual representation of SMMT, the type of a parameter is only shown if the parameter is of custom type. Hence, if the type of a parameter is not shown when the parameter of an *OnEvent* or a *DoEvent* is declared, then this parameter is of boolean type.

As shown in Figure 2.1, each SMMT specification has a section in which the *OnEvents* are defined that can be processed by the state machine of that SMMT specification. Similarly, the SMMT specification contains a section in which the *DoEvents* are defined that can be produced by the state machine of the SMMT specification.

(a) Textual Representation

(b) Graphical Representation

Figure 2.3: An SMMT specification of a printer that is idle or printing

We expand our running example with a state called printing and add OnEvents ev\_submit\_job(i: int) and ev\_finish\_job() that signal that the printer must start printing job i and that the printer must finish the job respectively. Furthermore, we add DoEvent alert\_started(i: int) that alerts the user that the printer has started printing job i. OnEvent ev\_submit\_job(i: int) and DoEvent alert\_started(i: int) have a parameter of custom type int called i which indicates the page of the job that must be printed. The extended running example is shown in Figure 2.3.

#### 2.2.3 Region

The *region* of an SMMT specification is hierarchically structured and consists of one or more states. Each state of the SMMT specification consists of several outgoing transitions, entry handlers, exit handlers and can contain a nested region. In the remainder of this section, we discuss the types of states, the transitions, entry- and exit handlers informally.

#### 2.2.3.1 State Types

The SMMT language supports four different types of states: *SimpleStates, CompositeStates, ParallelStates* and *JointStates*. The *execution state* of an SMMT specification consists of a subset of the states of the SMMT specification. We say that a state is an *active* state if, and only if, the state is an element of the execution state. We introduce the notion of an *entry* state. An *entry* state is a state that becomes active when the parent of that state is initiated. Each state, except for states of type *JointState*, can be an *entry* state. In the graphical representation of an SMMT specification, an entry state is indicated by the entry symbol ( $\leftarrow$ ).

To distinguish between the type of states in the SMMT specifications that are graphically depicted in the remainder of this report, we added a red prefix S, C, P or J in front of the name of each state. These red prefixes indicate the type of the state: *SimpleState, CompositeState, ParallelState* and *JointState* respectively. In the remainder of this section, we introduce each of the four different state types.

**SimpleState** States of type *SimpleState* represent states that have no children. In the running example (Figure 2.3), both states idle and printing are of type *SimpleState*.

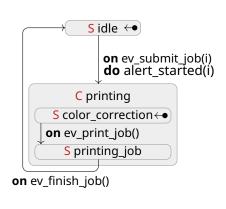

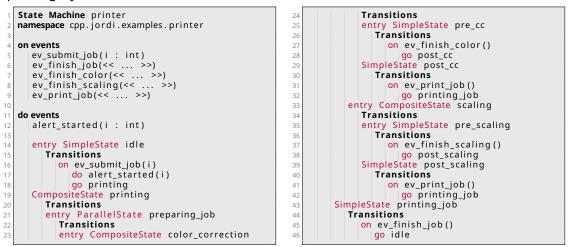

**CompositeState** The *CompositeState* type allows for children that further specify the behavior of the *CompositeState*. A *CompositeState* has one or more children of which exactly one is an entry state. Furthermore, if a *CompositeState* s is active, then exactly one child of *CompositeState* s must be active.

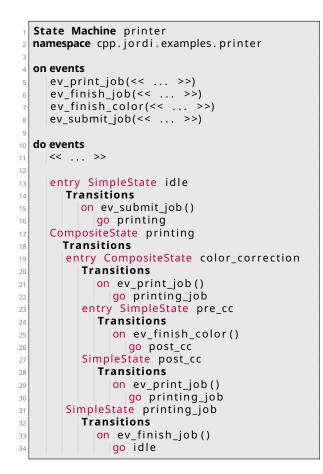

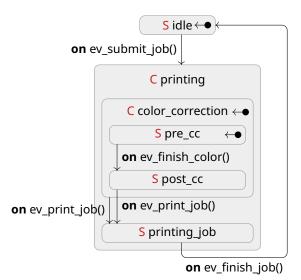

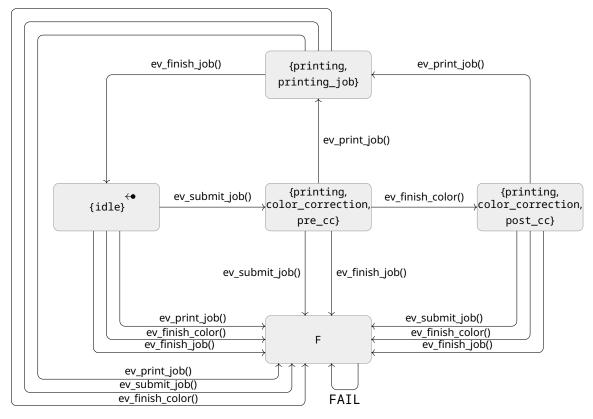

In our running example, a *CompositeState* can be used to further specify the behavior of the printing state. For example, we might need to apply color correction on the submitted job prior to printing the job. In Figure 2.4 we extend our running example of Figure 2.3 with states color\_correction and printing\_job. Furthermore, we add a transition from state color\_correction to state printing\_job for *OnEvent* ev\_print\_job() to ensure that the printer can only start printing the job whenever *OnEvent* ev\_print\_job() has been processed. In this example, state printing is a *CompositeState* and states idle, color\_correction and printing\_job are of type *SimpleState*.

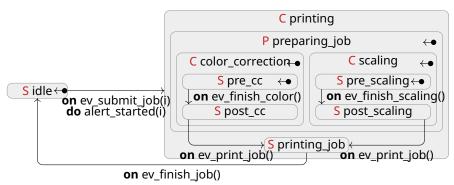

**ParallelState** States of type *ParallelState* have one or more children that further specify the behavior of the *ParallelState*. In contrast to *CompositeStates*, all children of a *ParallelState* are active as long as the *ParallelState* itself is active. Furthermore, all children of a *ParallelState* are entry states, except for the children of the *ParallelState* that are of type *JointState*.

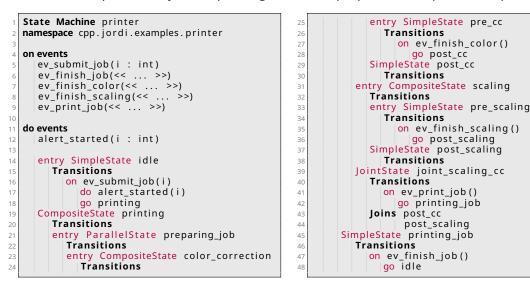

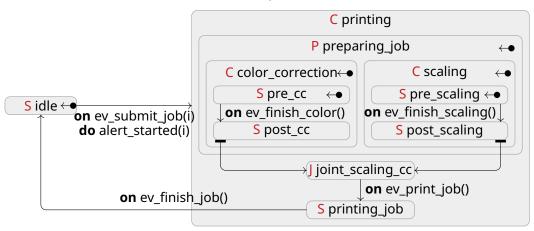

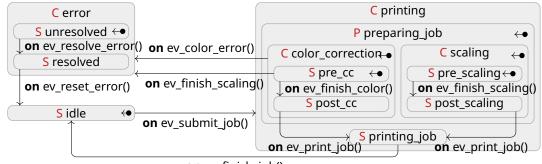

In the running example of Figure 2.4, a printer is shown that first applies color correction to a job after which the job gets printed. Using a *ParallelState* we can model that the printer applies color correction and scales the job in parallel, after which the job gets printed. In Figure 2.5, we extend the running example with *ParallelState* preparing\_job that allows the color correction and scaling of the job to be done simultaneously.

| 1<br>2 | State Machine printer<br>namespace cpp.jordi.examples.printer |  |  |  |  |  |  |  |  |  |  |  |  |

|--------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| 3      |                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

| 4      |                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

| 5      | ev_submit_job(i : int)                                        |  |  |  |  |  |  |  |  |  |  |  |  |

| 6      | ev_finish_job(<< >>)                                          |  |  |  |  |  |  |  |  |  |  |  |  |

| 7      | ev print job(<< >>)                                           |  |  |  |  |  |  |  |  |  |  |  |  |

| 8      | ev_print_job( ··· ··· )                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| 9      | do events                                                     |  |  |  |  |  |  |  |  |  |  |  |  |

| 10     | alert_started(i : int)                                        |  |  |  |  |  |  |  |  |  |  |  |  |

|        | alert_starteu(r . mt)                                         |  |  |  |  |  |  |  |  |  |  |  |  |

| 11     | lantus Cimula Stata idla                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| 12     | entry SimpleState idle                                        |  |  |  |  |  |  |  |  |  |  |  |  |

| 13     | Transitions                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| 14     | on ev_submit_job(i)                                           |  |  |  |  |  |  |  |  |  |  |  |  |

| 15     | <pre>do alert_started(i)</pre>                                |  |  |  |  |  |  |  |  |  |  |  |  |

| 16     | go printing                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| 17     | CompositeState printing                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| 18     | Transitions                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| 19     | entry SimpleState color_correction                            |  |  |  |  |  |  |  |  |  |  |  |  |

| 20     | Transitions                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| 21     | on ev_print_job()                                             |  |  |  |  |  |  |  |  |  |  |  |  |

| 22     | go printing_job                                               |  |  |  |  |  |  |  |  |  |  |  |  |

| 23     | SimpleState printing_job                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| 24     | Transitions                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| 25     | on ev_finish_job()                                            |  |  |  |  |  |  |  |  |  |  |  |  |

| 26     | go idle                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

|        |                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

(a) Textual Representation

(b) Graphical Representation

Figure 2.4: An SMMT specification consisting of a printer that applies color correction before printing a job

(a) Textual Representation

(b) Graphical Representation

Figure 2.5: An SMMT specification consisting of a printer that applies color correction and/or scales the job before printing the print job

Formalising the State Machine Modelling Tool (SMMT)

**JointState** States of type *JointState* are used to join the behavior of one or more nested states of a *ParallelState*. A *JointState* refers to several states but does not have any children itself and can only occur inside a *ParallelState*. Furthermore, a *JointState* may only refer to nested states or *JointStates* of the *ParallelState* in which the *JointState* occurs that can be active at the same point in time. A *JointState* is active when all states that the *JointState* refers to are active.

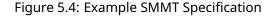

Consider the example in Figure 2.5. When the printer reaches the preparing\_job state, the printer starts to scale the document and apply color correction. However, in this example, as soon as either the color correction or scaling is completed, we are allowed to start printing the job when *OnEvent* ev\_print\_job() is processed. Suppose we want that both preparation steps are completed before the printer starts printing the job. To achieve this, a *JointState* can be used that refers to both states post\_cc and post\_scaling with an outgoing transition defined for *OnEvent* ev\_print\_job(). This only allows the printer to start printing if both the color correction process and scaling has been completed. In Figure 2.6, we extend the running example of Figure 2.5 with *JointState* joint\_scaling\_cc that ensures that the printer only starts printing after both preparation steps are completed.

(a) Textual Representation

(b) Graphical Representation

Figure 2.6: An SMMT specification consisting of a printer that applies color correction and scales the job before printing the job

#### 2.2.3.2 Transitions

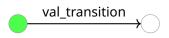

Zero or more outgoing transitions can be defined for each state of an SMMT specification. Each outgoing transition consists of an *OnEvent* for which the transition is defined and an optional target state. In case no target state is specified, the model interprets the transition as an internal transition, as indicated by the internal keyword. Furthermore, a guard and a list of *BehavioralActions* may be defined for each outgoing transition. A *BehavioralAction* is either a *DoEvent* that is produced as a response to the processed *OnEvent*, a *SelfPost* action to repost the *OnEvent* that was processed or a *Forward* action to allow the *OnEvent* to be handled by the ancestors of the state for which the *Forward* action is defined.

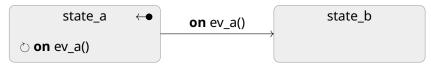

The difference between the representations of internal and external transitions are shown in Figure 2.7. In this example, the transition defined on lines 13 and 14 of the textual representation is an internal transition. The transition defined on lines 15 and 16 is an external transition. In the graphical representation of the SMMT specification, internal transitions are denoted using the self-loop icon  $\circlearrowright$  and are shown within the state for which the transition is defined. External transitions are shown with an arrow that exits and enters the state. When an external transition fires, the exit- and entry-handlers of the state are triggered if the transition is fired. Internal transitions do not trigger the exit- and entry-handlers of the state when the internal transition fires.

| State Machine printer<br>namespace cpp.jordi.examples.printer                            |                    |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|

| on events       b       ev_a(<< >>)       ev_b(<< >>)                                    | on ev_b()          |  |  |  |  |  |

| 8 <b>do events</b><br>9 <b>&lt; &gt;&gt;</b>                                             | S state ←●         |  |  |  |  |  |

| 10     entry SimpleState state       12     Transitions                                  | ဲ <b>on</b> ev_a() |  |  |  |  |  |

| 13     on ev_a()       14     go (internal)       15     on ev_b()       16     go state |                    |  |  |  |  |  |

(a) Textual Representation

(b) Graphical Representation

Figure 2.7: Representations of Internal and External Transitions

An outgoing transition of a state *s* that is defined for an *OnEvent e* fires if, and only if, state *s* is active when *OnEvent e* is processed and the guard of this transition evaluates to true. Furthermore, a transition from state *s* cannot fire if there exists a nested state of state *s* that has a transition that can fire that is defined for *OnEvent e*. When a transition fires, all *BehavioralActions* that are defined for this transition are produced. In Chapter 5 we formally define which transitions fire when an *OnEvent* is processed.

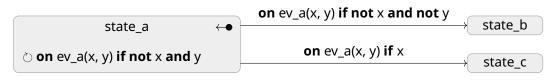

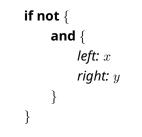

The guard of a transition is a boolean expression that may consist of the standard logical connectives (and, or and not), boolean literals (true and false) and references to the parameters of the *OnEvent* for which the transition is defined. SMMT allows references to custom typed parameters of the *OnEvent* for which the transition is defined in the guard. However, the generated C++ and C# code that is generated from the SMMT specification requires that the reference is of boolean type. No operators have been implemented in SMMT to compare the values of custom typed parameters. Hence, we cannot compare custom typed parameters and therefore references to custom type variables may cause errors in the generated C++ and C# code.

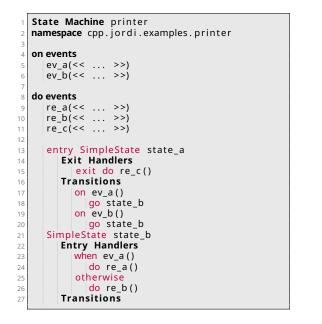

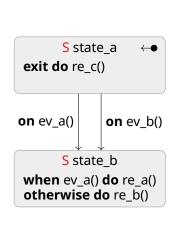

#### 2.2.3.3 Entry- and Exit-Handlers

For each state of an SMMT specification, zero or more entry- and exit-handlers can be defined. Entry- and exit-handlers model behavior that is performed when states are entered and exited respectively. In the following paragraphs we introduce the entry and the exit handlers and give an example of both.

**Entry Handlers** An entry handler specifies the actions that need to be performed when the state for which the entry handler is defined is entered. SMMT consists of two types of entry handlers: conditional entry handlers and otherwise entry handlers. Conditional entry handlers are entry handlers that are defined for an *OnEvent e* and state *s* that are triggered if, and only if, state *s* is entered by a transition defined for *OnEvent e*. An otherwise entry handlers that is defined for a state *s* fires if, and only if, state *s* is entered and no conditional entry handlers are triggered when state *s* is entered.

Both type of entry handlers consist of zero or more *DoEvent* and *Forward BehavioralActions* that are produced when the entry handler is triggered. Each entry handler can have a target state to which a transition is instantiated when the handler is triggered. Additionally, conditional entry handlers can consist of a *Forward BehavioralAction*. Finally, a guard can be defined for a conditional entry handler that restricts when the entry handler is triggered.

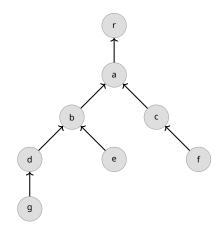

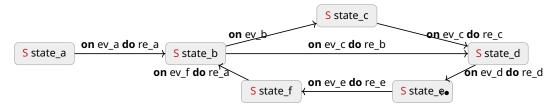

In Figure 2.8 an SMMT specification is shown that contains entry handlers. State state\_b contains both a conditional and otherwise entry handler. When state state\_a is active and *OnEvent* ev\_a() is processed, *DoEvent* re\_a() is produced on entry of state state\_b. Furthermore, if state state\_a is active and *OnEvent* ev\_b() is processed then *DoEvent* re\_b() is produced on entry of state state\_b, as there are no conditional entry handlers that are triggered by *OnEvent* ev\_b().

(a) Textual Representation

(b) Graphical Representation

**Exit Handlers** An exit handler specifies the actions that are performed when the state for which the exit handler is defined is exited. Each exit handler consists of zero or more *DoEvents* and *SelfPost BehavioralActions* that are produced when the exit handler is triggered. In contrast to entry handlers, exit handlers cannot be defined for a specific *OnEvent*, nor can they have guards, *Forward BehavioralActions* or a target state.

State state\_a of the SMMT specification shown in Figure 2.8 contains an exit handler. When state state\_a is active and either *OnEvent*  $ev_a()$  or  $ev_b()$  is processed, *DoEvent*  $re_c()$  is produced when the state is exited.

### 2.3 Execution

From the models that are designed using the State Machine Modelling Tool, executable C++ and C# code can be generated. The generated code makes use of the SCM library. In SMMT, the transitions of an SMMT specification are triggered when *OnEvents* are processed. *On*-*Events* are handled asynchronously using an event queue. A First-In-First-Out (FIFO) policy is used to dispatch the *OnEvents* in order of arrival. When an *OnEvent* occurs, the *OnEvent* is added to the end of the event queue. As soon as the first *OnEvent* is added to the queue, the *OnEvent* is processed by the SMMT specification.

When an *OnEvent* is processed, the replies are temporarily queued. Replies are the *BehavioralActions* that are produced in response to the received *OnEvents*. If the *OnEvent* cannot be handled by the SMMT specification, an internal software exception is thrown. Whenever an internal software exception is thrown, the execution of the SMMT specification is terminated. For all transitions that are fired due to the processed *OnEvent*, the respective exit handlers are triggered. Next, all queued replies are handled and the transition to the target states take place. For all states that were entered, the entry handlers are triggered and the entered states are initiated. This procedure repeats as long as there are *OnEvents* in the queue.

The execution state after an *OnEvent* has been processed is obtained by removing all states that cannot be active simultaneously with the target state of the transitions that fire. Next, all target states and ancestors of each target state of the transitions that fire are added to the execution state. Finally, the obtained execution state is initiated.

CHAPTER 2. STATE MACHINE MODELLING TOOL

## **Chapter 3**

## **Analysis of SMMT**

In this section we discuss our analysis on the State Machine Modelling Tool. We spoke with several engineers at Canon Production Printing that have used SMMT to model software components, as well as the engineer that developed the State Chart Modelling (SCM) library. In Section 3.1 we discuss the observations and experiences of the engineers at Canon Production Printing regarding the State Machine Modelling Tool. At Canon Production Printing, at the time of writing, the behavior of 26 software components have been modelled using SMMT. We discuss our analysis of the existing SMMT specifications in Section 3.2.

### 3.1 Observations and Experiences of Engineers

As mentioned before, we spoke with several engineers at Canon Production Printing that have used the State Machine Modelling Tool to model the behavior of software components. In this section we discuss the observations and experiences of the engineers at Canon Production Printing with SMMT that were shared by these engineers through interviews. We first discuss the insights that we gained through these meetings that are related to the language of the State Machine Modelling Tool. Next, we discuss the observations and experiences of the engineers regarding the implementation of SMMT in JetBrains MPS and the usage thereof. Finally, we briefly discuss the testing library of the SCM library that can be used to test the generated SCM code.

#### 3.1.1 Language of the State Machine Modelling Tool

The engineers that used the State Machine Modelling Tool unanimously agree that the tool greatly helps with the development of software components. Prior to the introduction of SMMT, the engineers were required to model the behavior of the software components directly using the State Chart Modelling (SCM) library or using the Boost C++ library [4, 5]. The State Chart Modelling library is a very powerful library that could directly be used by the engineers to model the behavior of software components. The absence of restrictions on the coding patterns and techniques that should be used by these engineers leads to a lack of uniformity between the developed executable code of different projects. The State Machine Modelling Tool ensures that the coding style and patterns of the code that are generated for each project are uniform. The State Machine Modelling Tool restricts the patterns that can be used to model the behavior of a software component. As a consequence, the executable code that is generated by the code generator of SMMT is uniform.

Most of the constructs of the SMMT language are deemed intuitive by the engineers that used the State Machine Modelling Tool. However, most of the engineers that were interviewed were unfamiliar with constructs like the *SelfPost* and *Forward BehavioralActions*.

The documentation only contains an explanation for the most frequently used constructs of the SMMT language. Constructs like the *SelfPost* and *Forward BehavioralActions* that are not understood by most engineers are either not explained in the documentation or are briefly discussed without any details.

In SMMT specifications with parallel behavior, there are usually multiple *JointStates* that perform the same behavior when executed but refer to different states. The number of *JointStates* grows quickly with the number of nested states of each *ParallelState*. As these *ParallelStates* tend to clutter the graphical representation of the SMMT specification, the engineers would prefer if *JointStates* that perform the same actions when executed could be merged using a join clause. This join clause would consist of the disjunction of the joined states of each *JointStates*.

#### 3.1.2 JetBrains MPS

The State Machine Modelling Tool has been implemented in the JetBrains MPS language workbench. JetBrains MPS is a language workbench that uses projectional editing. MPS projects the abstract syntax tree of an SMMT specification into a textual or graphical representation of the SMMT specification that can be edited by the engineer. The modifications that are made in the projections of the SMMT specification are direct modifications in the abstract syntax tree of that specification. In this section, we discuss the experiences and observations of the engineers regarding the usage of SMMT in JetBrains MPS.

**Learning Curve** In contrast to a textual editor, the engineer is not able to freely type code in the projections of the SMMT specification. Instead, engineers need to insert the constructs of SMMT through one of the projections. As most software engineers are familiar with textual editors, most engineers require some time to get familiar with projectional editing.

Without prior knowledge on how the engineer is supposed to work with MPS, editing an SMMT specification could be problematic, as inserting or editing constructs of an SMMT specification may require several key-binds to be used. For example, to add a transition from a state s to state t that fires for *OnEvent* e and produces *DoEvent* d we would need to perform the following steps:

- 1. Hover over the state *s*, select the transition icon and draw a transition to state *t*;

- 2. Select the transition and hit key-bind ctrl+space to select OnEvent e;

- 3. Select the transition and hit key-bind alt+enter to open the intentions menu;

- 4. Select "add action" and hit key-bind ctrl+space to select *DoEvent d*.

As shown by these four steps to add a single transition, the engineer must know various key-binds to edit an SMMT specification. This is one of the reasons why engineers that are inexperienced with MPS experience a steep learning curve when editing or creating SMMT specifications in MPS. As the interfaces of MPS are intuitive and the number of different key-binds that are used is limited, the engineers tend to familiarise themselves with MPS within several hours.

**Project Setup and Integration** To set up a new SMMT project, the engineers are required to go through a series of steps that are explained in the documentation of SMMT. There is no option inside MPS to directly set up a new SMMT MPS project. The process to set up a new project requires the copying and editing of various properties and build files. Due to the lack of an easy and quick way to set up a new SMMT project in MPS, engineers tend to avoid the use of the State Machine Modelling Tool when modelling simple software components, as the overhead of setting up a project would exceed the additional time it takes to manually implement the code using the SCM library.

The integration of the generated executable C++ and C# code is not documented in the documentation of the State Machine Modelling Tool. Neither does the documentation contain details on how the engineer is supposed to include the SCM library in the file, about how the state machine of the SMMT specification should be initiated or how the custom types and reply class should be defined.

**Projections of the SMMT Specification** The engineers unanimously agree that the graphical representation of SMMT is a great addition to the tool, especially when modelling the behavior of simple software component. However, the graphical representation is not powerful enough to get a clear overview of more complicated SMMT specifications.

The engineers that are familiar with the State Machine Modelling Tool observe that the behavior that is modelled by an SMMT specification is not always understood correctly by engineers that are less familiar with SMMT, especially for SMMT specifications that include parallel behavior. The engineers would like a projection in SMMT that would allow the engineers to model the parallel behavior in a less cluttered and more comprehensible manner. Such a projection would be beneficial for the engineers to understand SMMT specifications that include parallel behavior. Developing such a representation is outside the scope of this graduation project. Alternatively, a simulation tool to simulate the behavior of the SMMT specification.

The engineers observe that modifications to the projections of SMMT specifications are processed slowly. For example, when moving a state of an SMMT specification it may take a couple of seconds before the modification is saved and rendered. Furthermore, some modifications may break the SMMT specifications. The engineers observed that SMMT specifications broke when dragging states and transitions in the graphical representation of the SMMT specification. Furthermore, undoing and redoing actions may cause the SMMT specification to break.

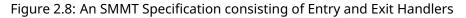

Due to the problems that arise when editing an SMMT specification in JetBrains MPS, engineers generally avoid SMMT when they model a simple software component that can easily be modelled directly using the SCM library. Furthermore, rather than directly using the State Machine Modelling Tool to model the behavior of software components, the state machine is in practice first modelled on paper or on a whiteboard after which it is digitalised using software like Draw.io, PlantUML or Enterprise Architect. When all feedback on the digitalised version of the state machine has been processed, the state machine is modelled using the State Machine Modelling Tool. A graphical overview of the modelling process that is used in practice is shown in Figure 3.1.

Figure 3.1: Graphical Overview of the Modelling Process

Optimally, the behavior of the software component would directly be modelled in an SMMT MPS project as this would be less time-consuming and less error-prone. In the current workflow, the state machine is modelled two times, both using external drawing software and in an SMMT MPS project. The external drawing software is considered to be more flexible than the graphical representation of MPS. Hence, the state machine is only modelled in an SMMT MPS project after the engineers have finalised the design of the state machine.

#### 3.1.3 SCM Test Library

The SCM library that is used by SMMT to generate executable C++ and C# code has a testing library that can be used to perform tests on the generated code. Using the SCM Test library, the engineers model the behavior of the state machine of the SMMT specification that they want to test as a separate state machine. To test if the behavior of the state machine that is tested is correct, the output channel of the test state machine and the input channel of the main state machine are coupled and vice versa. The test state machine sends *OnEvents* to the main state machine and listens to the *DoEvents* that are produced by the main state machine. In this way, the test state machine can verify whether the correct responses are received based on the produced *OnEvents*.

The engineers that were interviewed and were familiar with the SCM Testing library mentioned that the library is powerful to test whether the modelled behavior in the SMMT specification corresponds to what they expect. However, the engineers mention that there are limitations on the tests that can be run with the testing library.

Unfortunately, the SMMT tooling does not allow the engineers to generate tests automatically using the SCM test library. Therefore, the engineers must create these tests manually, which is a time-consuming process in which errors are easily made.

### 3.2 Analysis of Existing Models

At Canon Production Printing the State Machine Modelling Tool has been used to model the behavior of 26 software components. Table 3.2 shows an analysis on the structure of the SMMT specifications. The table shows for each construct how frequently it occurs in each SMMT specification. The names of the models have been replaced by the letters A to Z.

From the analysis of the structure of the existing SMMT specifications, we see that only 8 out of the 26 existing SMMT specifications include parallelism. That is, only specifications J, K, L, N, T, U, V and Z contain states of type *ParallelState*. As *JointStates* can only occur as a nested state of a *ParallelState*, there are also only 8 out of the 26 existing SMMT specifications that contain states of type *JointState*.

An important insight is that the *Forward* and *SelfPost BehavioralActions* do not occur in any of the 26 existing SMMT specifications. As mentioned before, the users of the SMMT tool that were interviewed were unfamiliar with the *Forward* and *SelfPost BehavioralActions*, which might explain why they are not used in the existing SMMT specifications.

The entry- and exit handlers only occur in the SMMT specifications that contain *Parallel-States*, except for SMMT specification Y. Out of the 26 existing SMMT specifications, there are only 3 specifications that contain conditional entry handlers. Furthermore, there exist only two SMMT specifications that contain exit handlers. The unfamiliarity of the software engineers with the entry- and exit handlers may explain why they are rarely used in practice.

### 3.3 Conclusion

The lack of documentation on the setup, the integration and the constructs of the State Machine Modelling Tool combined with the steep learning curve of JetBrains MPS has been found problematic for engineers that are unfamiliar with SMMT and MPS. However, engineers tend to get familiar with MPS rather quickly, therefore we leave this out of the scope for this graduation project. The lack of documentation on the language of SMMT is a more severe problem. The engineers that are responsible for maintaining SMMT should improve and extend the documentation that is currently available. The formal definition that is defined in Chapter 5 could be used as a basis to improve and extend the documentation of each of the constructs of SMMT.

| SMMT Specification | SimpleStates | CompositeStates | ParallelStates | JointStates | Total States | OnEvents | DoEvents | BooleanParameters | CustomTypeParameters | Transitions | DoEventActions | ForwardActions | SelfPostActions | Guards | Conditional Entry Handlers | Otherwise Entry Handlers | Exit Handlers |

|--------------------|--------------|-----------------|----------------|-------------|--------------|----------|----------|-------------------|----------------------|-------------|----------------|----------------|-----------------|--------|----------------------------|--------------------------|---------------|

| А                  | 48           | 8               | 0              | 0           | 56           | 51       | 80       | 2                 | 35                   | 129         | 149            | 0              | 0               | 8      | 0                          | 0                        | 0             |

| В                  | 16           | 2               | 0              | 0           | 18           | 22       | 17       | 2                 | 0                    | 28          | 24             | 0              | 0               | 2      | 0                          | 0                        | 0             |

| С                  | 17           | 3               | 0              | 0           | 20           | 21       | 18       | 1                 | 0                    | 56          | 45             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| D                  | 20           | 4               | 0              | 0           | 24           | 21       | 21       | 1                 | 0                    | 67          | 50             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| Е                  | 14           | 2               | 0              | 0           | 16           | 19       | 18       | 1                 | 6                    | 30          | 33             | 0              | 0               | 2      | 0                          | 0                        | 0             |

| F                  | 13           | 2               | 0              | 0           | 15           | 18       | 18       | 1                 | 6                    | 27          | 28             | 0              | 0               | 2      | 0                          | 0                        | 0             |

| G                  | 9            | 1               | 0              | 0           | 10           | 12       | 9        | 1                 | 0                    | 18          | 13             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| Н                  | 9            | 1               | 0              | 0           | 10           | 11       | 8        | 1                 | 0                    | 18          | 11             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| Ι                  | 6            | 0               | 0              | 0           | 6            | 6        | 4        | 1                 | 0                    | 7           | 6              | 0              | 0               | 0      | 0                          | 0                        | 0             |

| J                  | 32           | 7               | 1              | 5           | 45           | 38       | 38       | 8                 | 2                    | 67          | 63             | 0              | 0               | 18     | 0                          | 8                        | 0             |

| К                  | 26           | 6               | 1              | 14          | 47           | 35       | 35       | 3                 | 2                    | 59          | 63             | 0              | 0               | 8      | 0                          | 14                       | 0             |

| L                  | 49           | 10              | 1              | 23          | 83           | 55       | 41       | 8                 | 8                    | 133         | 100            | 0              | 0               | 16     | 0                          | 9                        | 0             |

| М                  | 12           | 3               | 0              | 0           | 15           | 16       | 13       | 4                 | 0                    | 31          | 30             | 0              | 0               | 8      | 0                          | 0                        | 0             |

| Ν                  | 14           | 3               | 1              | 13          | 31           | 8        | 12       | 0                 | 0                    | 15          | 19             | 0              | 0               | 0      | 3                          | 18                       | 0             |

| 0                  | 14           | 1               | 0              | 0           | 15           | 20       | 15       | 2                 | 0                    | 25          | 22             | 0              | 0               | 2      | 0                          | 0                        | 0             |

| Р                  | 12           | 0               | 0              | 0           | 12           | 10       | 11       | 0                 | 0                    | 14          | 14             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| Q                  | 4            | 0               | 0              | 0           | 4            | 5        | 4        | 4                 | 0                    | 20          | 6              | 0              | 0               | 6      | 0                          | 0                        | 0             |

| R                  | 2            | 0               | 0              | 0           | 2            | 4        | 1        | 1                 | 0                    | 8           | 4              | 0              | 0               | 0      | 0                          | 0                        | 0             |

| S                  | 9            | 1               | 0              | 0           | 10           | 8        | 5        | 3                 | 0                    | 32          | 19             | 0              | 0               | 10     | 0                          | 0                        | 0             |

| Т                  | 17           | 9               | 2              | 3           | 31           | 15       | 8        | 3                 | 0                    | 34          | 12             | 0              | 0               | 2      | 0                          | 6                        | 1             |

| U                  | 27           | 13              | 1              | 9           | 50           | 22       | 14       | 7                 | 0                    | 80          | 24             | 0              | 0               | 20     | 0                          | 18                       | 0             |

| V                  | 22           | 6               | 1              | 9           | 38           | 13       | 15       | 2                 | 16                   | 40          | 16             | 0              | 0               | 6      | 2                          | 19                       | 2             |

| W                  | 30           | 1               | 0              | 0           | 31           | 24       | 39       | 0                 | 0                    | 72          | 68             | 0              | 0               | 0      | 0                          | 0                        | 0             |

| Х                  | 5            | 0               | 0              | 0           | 5            | 4        | 4        | 1                 | 0                    | 18          | 5              | 0              | 0               | 2      | 0                          | 0                        | 0             |

| Y                  | 5            | 1               | 0              | 0           | 6            | 7        | 7        | 1                 | 17                   | 13          | 12             | 0              | 0               | 0      | 1                          | 0                        | 0             |

| Z                  | 14           | 3               | 1              | 13          | 31           | 8        | 8        | 0                 | 0                    | 15          | 12             | 0              | 0               | 0      | 0                          | 18                       | 0             |

| $\sum$             | 446          | 87              | 9              | 89          | 631          | 473      | 463      | 58                | 92                   | 1056        | 848            | 0              | 0               | 112    | 6                          | 110                      | 3             |

Figure 3.2: Structural Analysis on the existing SMMT Specifications

Based on the analysis of the existing SMMT specifications, we define the following order in which the constructs of SMMT are formalised: *SimpleStates, CompositeStates,* Transitions (without guards and *BehavioralActions*), *ParallelStates, JointStates,* Transitions (with guards and *DoEvents*), Otherwise Entry Handlers, Conditional Entry Handlers and Exit Handlers. Due to a lack of time, the *SelfPost BehavioralActions* and *Forward BehavioralActions* are not supported by the translation that we have defined.

The projections of the SMMT Specifications that exist in the State Machine Modelling Tool are sufficient for visualizing simple SMMT specifications but are not powerful enough to visualize the parallel behavior of SMMT specifications. A visualization that could visualize the parallel behavior of an SMMT specification would help the engineers to understand the SMMT specification. Alternatively, a simulation tool could help as well in understanding an SMMT specification. Using the mCRL2 language and toolset, LTSs can be generated that visualise the behavior of an SMMT specification. Furthermore, the toolset contains a tool that can be used to simulate the behavior of the mCRL2 specification. Unfortunately, this does not allow the engineer to simulate the SMMT specification in MPS directly. Having a simulation tool within MPS that would simulate the SMMT specification using for example the graphical representation of the SMMT specification would be more beneficial for the engineers. Nevertheless, the views that can be generated using the mCRL2 toolset and the simulation tool of the mCRL2 toolset can be useful for the engineers to debug and analyse the behavior of the SMMT specification that they modelled.

The SCM library that is used by the generated executable code consists of a testing library that can be used to perform tests on the generated code. However, the test cases that can be defined using this testing library are limited. This shows why expanding the State Machine Modelling Tool with a translation to mCRL2 specifications is beneficial, as the mCRL2 toolset allows us to verify properties on the mCRL2 specification that cannot be verified using the testing library of the SCM library. Furthermore, as the tests that are defined using the SCM testing library cannot be generated from SMMT and thus must be defined manually, testing is a time-consuming and error-prone task. Using an automated translation to mCRL2 specifications, these properties can automatically be tested on the mCRL2 specification. A disadvantage of performing tests via mCRL2 specifications is that this requires the engineers to know how properties can be expressed as a modal mu-calculus formula.

## **Chapter 4**

## **Mathematical Preliminaries**

In Chapter 5 we formally define the SMMT language. To define the syntax and semantics of SMMT specifications, we need to introduce some definitions. We first define the notation used for lists and define the *unique existential quantifier*. We define a *child relation* and define the notion of a *subregion*. Finally, we define *labelled transition systems* (LTSs) that are used to define the semantics of an SMMT specification.

First we define some notation that is used in the remainder of this report to reason about lists. The length of a list  $\mathbb{L}$  is denoted by  $|\mathbb{L}|$ . We write  $\mathbb{L}[i]$  to denote the value in list  $\mathbb{L}$  at index i, where  $0 \le i < |\mathbb{L}|$ . The first element in a list has index 0. We write  $x \in \mathbb{L}$  if there exists an index  $i, 0 \le i < |\mathbb{L}|$ , such that  $\mathbb{L}[i] = x$ .

We define the *unique existential quantifier* to express whether there exists exactly one element in the domain that satisfies a predicate.

**Definition 1** (Unique Existential Quantifier). Let *X* be a set of variables and let P(x) be a predicate over a variable  $x \in X$ . The *unique existential quantifier*, denoted by  $\exists$ !, is defined as follows:

$(\exists !_{x \in X} : P(x)) \Leftrightarrow (\exists_{x \in X} : (P(x) \land (\neg \exists_{x' \in X} : P(x') \land x \neq x')))$

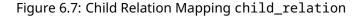

We define a *child relation* that defines how the states in a hierarchically structured setting are related. This relation allows us to reason about the *children*, *parent*, *descendants* and *ancestors* of a state in a set of states.